### IMSAI

## MOTHERBOARD

Copyright © 2002

IMSAI Division

Fischer-Freitas Company

Orangevale, CA 95662

Made in the U. S. A.

All rights reserved worldwide

#### MOTHER BOARD

#### FUNCTIONAL DESCRIPTION

The IMSAI 8080 system Mother boards are available in three different length sections varying from a minimum of 4 printed circuit card connector positions. The basic system includes a Mother board with six connector positions on it. One is used for the front panel and the other five are available for the MPU and any combination of memory or I/O cards.

The card-to-card spacing on the Mother board is 3/4 inch except for the front position which is reserved for the front panel board or the parallel I/O board for the dedicated processor to accommodate mounting the card in the special front position in the cabinet.

Additional sections of Mother board are available with positions for 4 connectors. These may be added to the system at a later date, and connected to the previous Mother board sections by jumpers between the sections soldered into provided holes. No jumper wire soldering is required if the full-length board is purchased.

The Mother board is 1/16 inch printed circuit board with double-sided plated-through holes. Each of the connector pins is connected by traces on both sides of the board. Heavy power traces are provided to handle the very large currents involved in a fully-loaded back plane. The two connectors supplied with the IMSAI system are high-quality gold-plated-contact connectors, for reliable contacts and long life.

Trace spacing is tightly controlled on the board to avoid any close spots where shorts from solder bridges might tend to occur. The traces on Mother board are plated for better appearance and more reliable solder connections. A solder mask is provided on both sides of the Mother board.

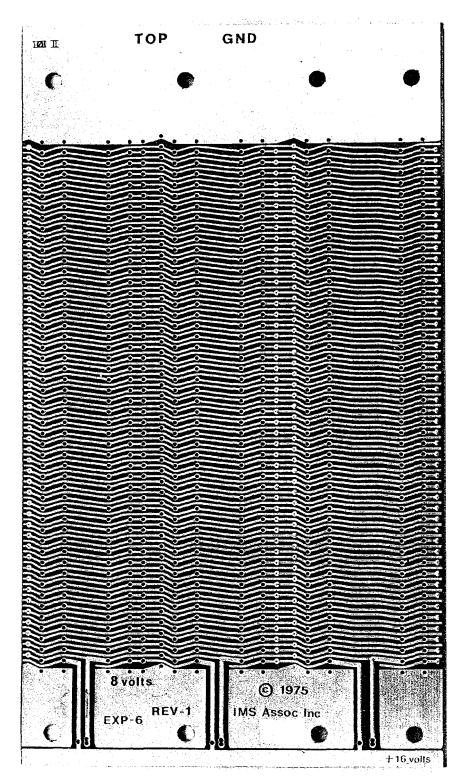

EXP-6

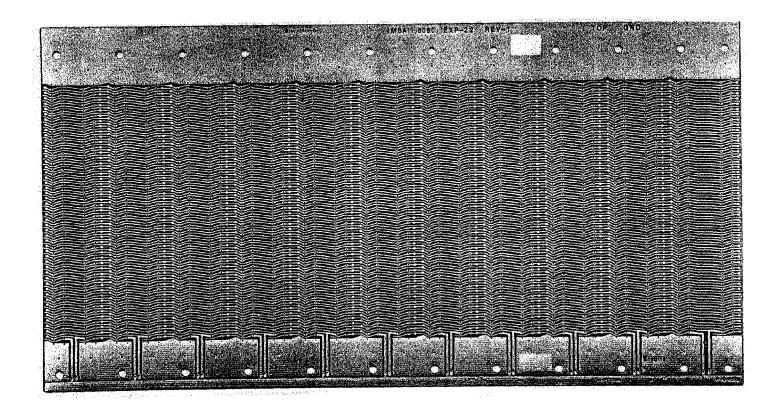

EXP-22 Rev. 1

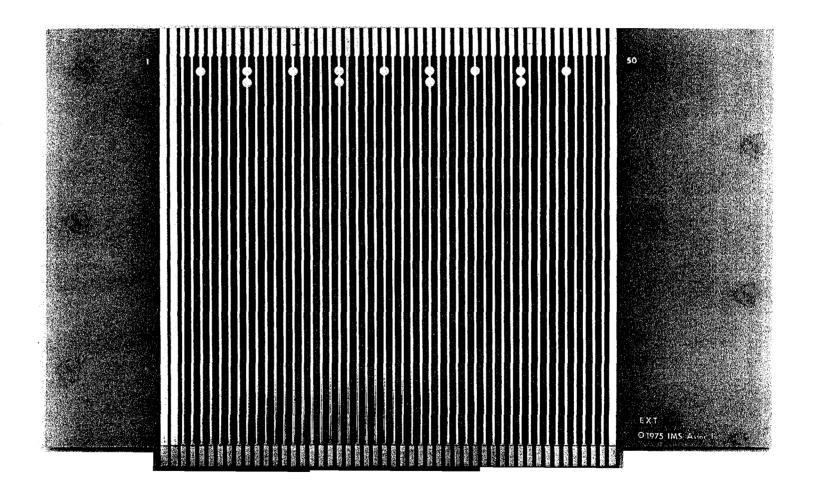

EXT (EXTENDER BOARD)

## Mother Board Parts List

# EXP-4

| <u>ITEM</u> | IMSAI<br>PART # | QUANTITY | DESCRIPTION/IDENTIFYING MARKS |

|-------------|-----------------|----------|-------------------------------|

| PC Board    | 92-0000004      | 1        | 4-Slot Printed Circuit Board  |

| Washer      | 21-3330001      | 8        | #6 Sholder Fiber Washer       |

| Spacer      | 21-4600001      | 4        | 6-32x4" Threaded Spacer       |

| Nut         | 21-3120001      | . 4      | 6-32 Nut                      |

| Screw       | 20-3701002      | 4        | 6-32x3/4" Nylon Screw         |

| EXP-6       | •               |          |                               |

| PC Board    | 92-0000005      | 1 -      | 6-Slot Printed Circuit Board  |

| Washer      | 21-3330001      | . 16     | #6 Shoulder Fiber Washer      |

| Spacer      | 21-4600001      | . 8      | 6-32x1" Threaded Spacer       |

| Nut         | 21-3120001      | . 8      | 6-32 Nut                      |

| Screw       | 20-3701002      | 8        | 6-32x3/4" Nylon Screw         |

| EXP-22      | •               |          |                               |

| PC Board    | 92-0000006      | 1 :      | 22-Slot Printed Circuit Board |

| Wahser      | 21-3330001      | 48       | #6 Shoulder Fiber Washer      |

| Spacer      | 21-4600001      | 24       | 6-32x4" Threaded spacer       |

| Nut         | 21-312000]      | L 24     | 6-32 Nut                      |

| Screw       | 20-3701002      | 2 24     | 6-32x3/4" Nylon screw         |

#### MOTHER BOARD

#### ASSEMBLY INSTRUCTIONS

The Mother board appears to be the simplest of all the boards to assemble. The solder mask minimizes the chances of shorting adjacent traces. However, it is imperative that extra care be taken during assembly to avoid excess solder shorting adjacent pins. Because a short on the Mother board is extremely hard to locate and correct when it is between the board and the connector, it is worth the builder's time to give special attention to making certain that no such shorts occur. Use only as much solder as required for a good joint. If too much solder is used, either the pool of solder can short to an adjacent pin on the top side or the solder can leak through and form a ball on the backside which can also short to an adjacent pin.

The board should be checked with an ohmmeter carefully both before and after assembly to insure that it will operate properly. While the chance that incomplete etching during manufacture left two traces shorted is extremely slight, the ohmmeter check before assembly is worth while simply because it would be so difficult to correct such a problem after a socket is soldered in place over it.

To test the board, either a simple ohmmeter or a battery connected to a buzzer or a light bulb and test leads are all that is required. Each pair of adjacent traces should be checked with the continuity tester to be sure that there is no connection between them. Should any adjacent traces be found to be electrically connected during this pre-assembly check, careful inspection of the board should reveal the short. Any imcompletely-etched copper or other metallic path between the two traces shold be removed with a sharp knife, such as an X-acto knife.

After each connector is soldered in, the continuity check should be made again to make certain that during assembly no shorts were created. If any are discovered, steps should be taken to remove them before further assembly. In most cases, this short will have been caused by too much solder having been applied and may be removed simply by removing the excess solder. If an Extender board is available, a simple tester may be made from it by temporarily connecting all the pins on the front side, except pin 1, together, connecting all the pins on the back side, except pin 100, together and then connecting the continuity tester between the two sides of the Extender board. If this extender board is inserted in the socket as it is being soldered, the continuity tester will indicate immediately any short between any two adjacent traces.

### Mother Board Assembly Instructions

### SOCKET INSERTION

The 100 pin edge connectors are symmetrical so that they may be inserted either way. The connector stands off the board slightly supported by raised feed at each end. Each connector should be checked during assembly to make sure that it is seated properly and that the Mother board near the center of the connector is neither pushed further toward the connector nor lifted away before the connector is soldered in place to prevent the Mother board from bowing.

The Mother board is not completely symmetrical and the connectors must be inserted from the top side. The top side is the side on which the +8 volt foil is broken every 2 connectors to allow the 2 traces for + and -16 volts to extend from the 16 volt bus at the end of the board into the connector pins. The back side of the board has both the very heavy ground bus and the 1 inch wide 8 volt foil area continuous for the full length of the board. volt trace is the .2 inch trace on the edge of the board alongside the +8 volt bus on the front side, that is, the side where the +8 is broken to allow for the pairs of +16 volt traces to extend into the pins. The -16 volt bus is the .2 inch wide trace along the edge of the board on the back side underneath the +16 volt bus. NOTE: Before mounting any connectors, locate the front of the Mother board. The connector for the front panel (CPA board) needs to be mounted in the first position at the front of the Mother board. Notice that the spacing between the first and second positions at the front of the Mother board is wider than the spacing between any two of the other connector positions.

The suggested procedure for inserting and soldering a connector is to insert the connector in place, seat the two ends firmly against the feet and solder the two pins on each end.

Next, the position of the center of the Mother board next to the connector should be checked and either pushed further toward the connector or pulled away so that the gap between the connector and the Mother board is uniform all the way across. Then the two pins in the center of the connector should be soldered.

One final check should be made to make sure that the gap is uniform all the way across the connector and the remaining pins in the connector should be soldered.

Care should be taken to check each connector after solder to make sure that every pin was soldered because it is easy to miss a pin and not see it during a quick inspection. After the last connector is soldered in place and the board checked you are ready to install the power connections and mount the board in the cabinet.

See MAINFRAME ASSEMBLY section for connecting the Mother board to the Power Supply and mounting the Mother board in the chassis.

### Mother Board

### USER GUIDE

With the proper care taken during assembly, the Mother board should be the most reliable board in the system. The only attention the user will typically put on the Mother board, is when he desires to add more card slot positions. Either 4 slot extension Mother Boards may be added to the original 6 slot Mother Board, or the 6 slot board may be replaced by a new 22 slot board.

If 4 slot extension(s) are used, the extension(s) should be assembled according to instructions for assembling the original Mother board. Then the original Mother board must be removed from the cabinet and jumpered to the new section by the use of short wire jumpers between the connection points provided in each trace.

The power buses should be connected with a much heavier wire. The two boards can then be reassembled into the cabinet.

Care should be taken when inserting jumpers that each goes between the corresponding lines on the two sections of Mother board.

# IMSAI 8080 BUS SIGNAL LIST

| _1.i     | +8 <b>y</b>    |

|----------|----------------|

| 2        | +16v           |

| 3        | XRDY           |

| 4        | VIO            |

| 5        | VII            |

| 6        | VI 2           |

| 7        | VI 3           |

| 8        | VI 4           |

| 9        | VI 5           |

| -        |                |

| 10<br>11 | VI 6<br>VI 7   |

| 12       |                |

|          |                |

| 13       |                |

|          |                |

| 15       |                |

| 16<br>17 |                |

|          |                |

| 18       | STATUS DSBL    |

| 19       | CCDSBL         |

| 20       | SS             |

| 21<br>22 |                |

| 23       | ADDR DSBC      |

| 24       | DO D2RF        |

| 25       | 02             |

|          | Ø1             |

| 26<br>27 | PHLDA<br>PWAIT |

| 28       | PINTE          |

| 29       | A 5            |

| 30       | A 4            |

| 31       | A 3            |

| 32       | A 15           |

| 33       | A 12           |

| 34       | A 12<br>A 9    |

| 35       | DO 1           |

| 36       | DO             |

| 37       | A 10           |

| 38       | DO 4           |

| 39       | DO 5           |

| 40       | DO 6           |

| 41       | DI 2           |

| 42       | DI 3           |

| 43       | DI 7           |

| 44       | SMI            |

| 45       | SOUT           |

| 46       | SINP           |

| 47       | SMEMR          |

| 48       | SHLTA          |

| 49       | CLOCK (2 MHz)  |

| 50       | GND            |

|          | 1 0110         |

| <u></u>  |               |

|----------|---------------|

| 51       | +8v           |

| 52       | -16v          |

| 53       | SSW DSB       |

| 54       | EXTCLR        |

| 55       | <u> </u>      |

| 56       |               |

| 57       |               |

| 58       |               |

| _59_     |               |

| _60_     | <u> </u>      |

| 61       |               |

| 62       |               |

| 63       |               |

| 64       |               |

| 65       |               |

| 66       | ļ             |

| 67       | 10000         |

| 68       | MWRITE        |

| 69       | ***           |

| 70       | • 1           |

| 71       | RUN           |

| 72       | PRDY          |

| 73       | PINT          |

| 74       | PHOLD         |

| 75       | PRESET        |

| 76       | PSYNC         |

| 77       | PWR           |

| 78       | POBIN         |

| 79       | A 0           |

| 80<br>81 | A 1<br>A 2    |

|          |               |

| 82       | A 6           |

| 83       | A 7<br>A 8    |

| 84       | A 13          |

| 85       |               |

| 86       | A 14<br>A 11  |

| 88       | DO 2          |

| 89       | DO 3          |

| 90       | DO 7          |

| 91       | DI 4          |

| 92       | DI 5          |

| 93       | DI 6          |

| 94       |               |

| 95       | DI 1          |

| 96       | SINTA         |

| 97       | SWO           |

| 98       | SWO<br>SSTACK |

| 98       | POC           |

| 100      | GND           |

| 100      | ן טויט        |

|          |               |

<sup>\*</sup> reserved for chassis ground \*\* reserved for memory unprotect \*\*\* reserved for memory protect \*\*\*\* reserved for protect status

| Front Si | ide<br>SYMBOL | NAME             | FUNCTION                                                                                                                                                                                                                                      |

|----------|---------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22       | ADDR DSBL     | ADDRESS DISABLE  | Allows the buffers<br>for the 16 address<br>lines to be tri-<br>stated                                                                                                                                                                        |

| 23       | DO DSBL       | DATA OUT DISABLE | Allows the bidirectional data bus drivers for the 8 data lines to be tristated for both input and output data buses                                                                                                                           |

| 24       | Ø2            | Phase 2 Clock    |                                                                                                                                                                                                                                               |

| 25       | Ø1            | Phase 1 Clock    |                                                                                                                                                                                                                                               |

| 26       | PHLDA         | Hold Acknowledge | Processor control output signal which appears in response to the HOLD signal; indicates that the data and address bus will go to the high impedance state on the 8080. Note:  ADDR DSBL and DO DSBL must be driven to ri-state the system bus |

| 27       | PWAIT         | WAIT             | Processor control output signal which acknowledges that the processor is in a WAIT state                                                                                                                                                      |

| 28       | PINTE         | INTERRUPT ENABLE | Processor control output signal indicating interrupts are enabled: may be set or reset by EI and DI instruction and inhibits interrupts from being accepted by the CPU if it is reset                                                         |

| Front Side | SYMBOL | NAME             | FUNCTION                                                                                                                                                            |

|------------|--------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29         | A5     | Address Line #5  |                                                                                                                                                                     |

| 30         | A4     | Address Line #4  |                                                                                                                                                                     |

| 31         | A3     | Address Line #3  |                                                                                                                                                                     |

| 32         | A15    | Address Line #15 |                                                                                                                                                                     |

| 33         | A12    | Address Line #12 |                                                                                                                                                                     |

| 34         | А9     | Address Line #9  |                                                                                                                                                                     |

| 35         | DO     | Data Out Line #1 |                                                                                                                                                                     |

| 36         | DO0    | Data Out Line #0 |                                                                                                                                                                     |

| 37         | A10    | Address Line #10 |                                                                                                                                                                     |

| 38         | DO4    | Data Out Line #4 |                                                                                                                                                                     |

| 39         | DO5    | Data Out Line #5 |                                                                                                                                                                     |

| 40         | D06    | Data Out Line #6 |                                                                                                                                                                     |

| 41         | D12 :  | Data In Line #2  |                                                                                                                                                                     |

| 42         | D13    | Data In Line #3  |                                                                                                                                                                     |

| 43         | D17    | Data In Line #7  |                                                                                                                                                                     |

| 44         | SM1    | Ml               | Status output signal that indicates that the processor is in the fetch cycle for the first byte of an instruction                                                   |

| 45         | SOUT   | OUT <sub>.</sub> | Status output signal which indicates that the address bus contains the address of an output device and the data bus will contain the output data when PWR is active |

| Front Sid | e<br>SYMBOL | NAME                    | FUNCTION                                                                                                                                                                        |

|-----------|-------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 46        | SNIP        | INP                     | Status output signal which indicates that that the address bus contains the address of an input device and the input data should be placed on the data bus when PDBIN is active |

| 47        | SMEMR       | MEMR                    | Status output signal which indicates that the data bus will be used for memory read data                                                                                        |

| 48        | SHLTA       | HLTA                    | Status output signal which acknowledges a HALT instruction                                                                                                                      |

| 49        | CLOCK       | CLOCK                   | 2 MHz clock signal                                                                                                                                                              |

| 50        | GND         | GROUND                  |                                                                                                                                                                                 |

| Back Side | •           |                         |                                                                                                                                                                                 |

| No.       | SYMBOL      | NAME                    | FUNCTION                                                                                                                                                                        |

| 51        | +8V         | +8 volts                | Unregulated input to 5v regulators                                                                                                                                              |

| 52        | -16V        | -16 volts               | Negative unregulated voltage                                                                                                                                                    |

| 53        | SSW DSB     | SENSE SWITCH<br>DISABLE | Disables the data in-<br>put buffers so the<br>input from the sense<br>switches may be<br>strobed onto the bi-<br>directional data bus                                          |

| 54        | EXT CLR     | EXTERNAL CLEAR          | Clear signal for I/O devices (front panel switch closure to ground)                                                                                                             |

| Back Side      | SYMBOL | NAME           | FUNCTION                                                                                                                                                                                            |

|----------------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55             | CGND   | CHASSIS GROUND |                                                                                                                                                                                                     |

| 56<br>to<br>67 | UNUSED |                |                                                                                                                                                                                                     |

| 68             | MWRT   | MEMORY WRITE   | From the Front Panel indicates that the current data on the Data Out Bus is to be written into the memory location currently on the address bus                                                     |

| 69             | PS     | PROTECT STATUS | Reserved to indicate the status of the memory protect flip-flop on the memory board currently addressed                                                                                             |

| 70             | PROT   | PROTECT        | Reserved for input<br>to the memory protect<br>flip-flop on the<br>memory board current-<br>ly addressed                                                                                            |

| 71             | RUN    | RUN            | Indicates that the RUN/STOP flip-flop is set to run on the front panel                                                                                                                              |

| 72             | PRDY   | READY          | Processor command/<br>control input that<br>controls the run<br>state of the pro-<br>cessor; if the line<br>is pulled low the<br>processor will enter<br>a wait state until<br>the line is released |

| Back Side |        |                      |                                                                                                                                                                                                                                                      |

|-----------|--------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.       | SYMBOL | NAME                 | FUNCTION                                                                                                                                                                                                                                             |

| 73        | PINT   | INTERRUPT<br>REQUEST | The processor recognizes an interrupt request on this line at the end of the current instruction or while halted. If the processor is in the HOLD state or the Interrupt Enable flip-flop is reset, it will not honor the request                    |

| 74        | PHOLD  | HOLD                 | Processor command input signal which requests the processor to enter the HOLD state; allows an external device to gain control of address and data buses as soon as the processor has completed its use of these buses for the current machine cycle |

| 75        | PRESET | RESET                | Processor command input; while activated the content of the program counter is cleared and the instruction register is set to 0                                                                                                                      |

| 76        | PSYNC  | SYNC                 | Processor control output provides a signal to indicate the beginning of each machine cycle                                                                                                                                                           |

| 77        | PWR    | WRITE                | Processor control output used for memory write or I/O output control; continued next page.                                                                                                                                                           |

| Back Side |        |                  |                                                                                                       |

|-----------|--------|------------------|-------------------------------------------------------------------------------------------------------|

| No.       | SYMBOL | NAME             | FUNCTION                                                                                              |

| 77        | PWR    | WRITE            | Con't.: data on the data bus is stable while the PWR is active                                        |

| 78        | PDBIN  | DATA BUS IN      | Processor control output signal indicates to external circuits that the data bus is in the input mode |

| 79        | A0     | Address Line #0  |                                                                                                       |

| 80        | A1     | Address Line #1  |                                                                                                       |

| 81        | A2     | Address Line #2  |                                                                                                       |

| 82        | A6     | Address Line #6  |                                                                                                       |

| 83        | A7     | Address Line #7  |                                                                                                       |

| 84        | A8     | Address Line #8  |                                                                                                       |

| 85        | A13    | Address Line #13 |                                                                                                       |

| 86        | A14    | Address Line #14 |                                                                                                       |

| 87        | A11    | Address Line #11 |                                                                                                       |

| 88        | DO2    | Data Out Line #2 |                                                                                                       |

| 89        | DO3    | Data Out Line #3 |                                                                                                       |

| 90        | DO7    | Data Out LIne #7 |                                                                                                       |

| 91        | D14    | Data In Line #4  |                                                                                                       |

| 92        | D15    | Data In Line #5  |                                                                                                       |

| 93        | D16    | Data In Line #6  |                                                                                                       |

| 94        | D17    | Data In Line #1  |                                                                                                       |

| 95        | D10    | Data In Line #0  |                                                                                                       |