CompuPro Interfacer1

Introduction

This board incorporates reliable LSI technology UART chips to perform the basic serial-to-parallel and parallel-to-serial conversions necessary for this S-100 dual channel I/O board. By using these UARTs, the CPU is freed of the time consuming drudgery of performing serial I/O operations by software techniques. Because of this, I/O operations are far more reliable and easier to implement. [1]

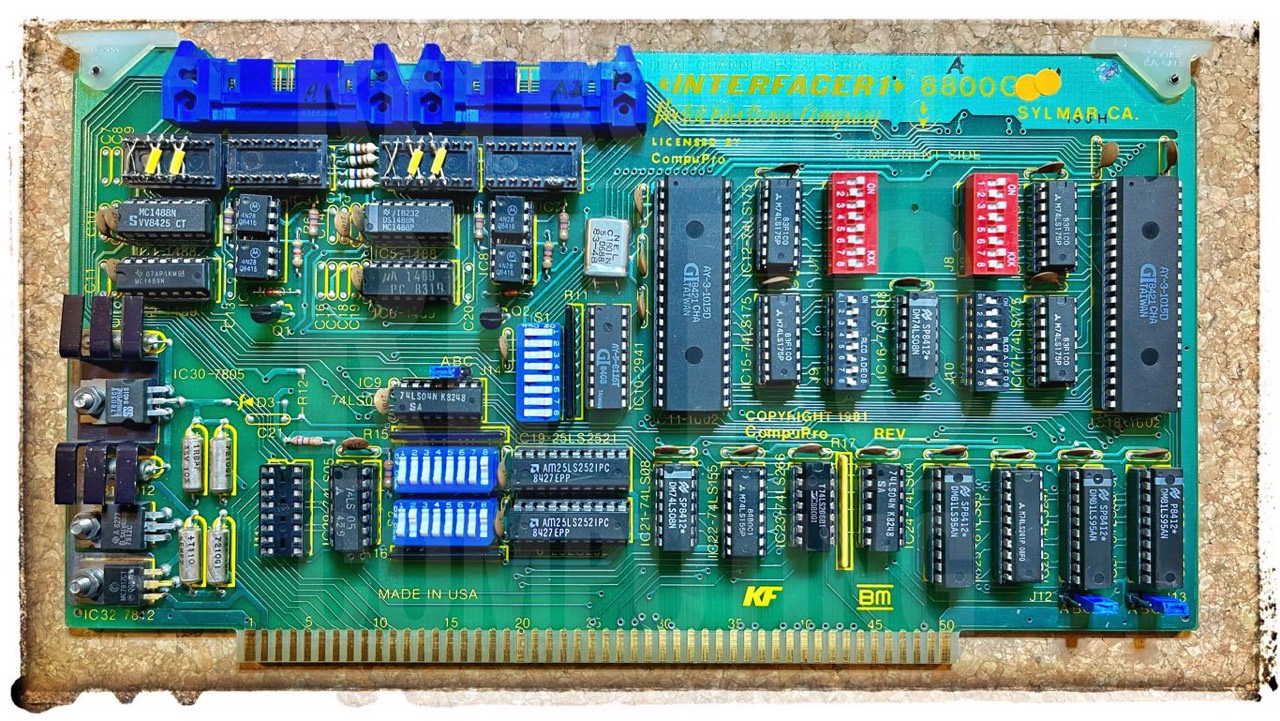

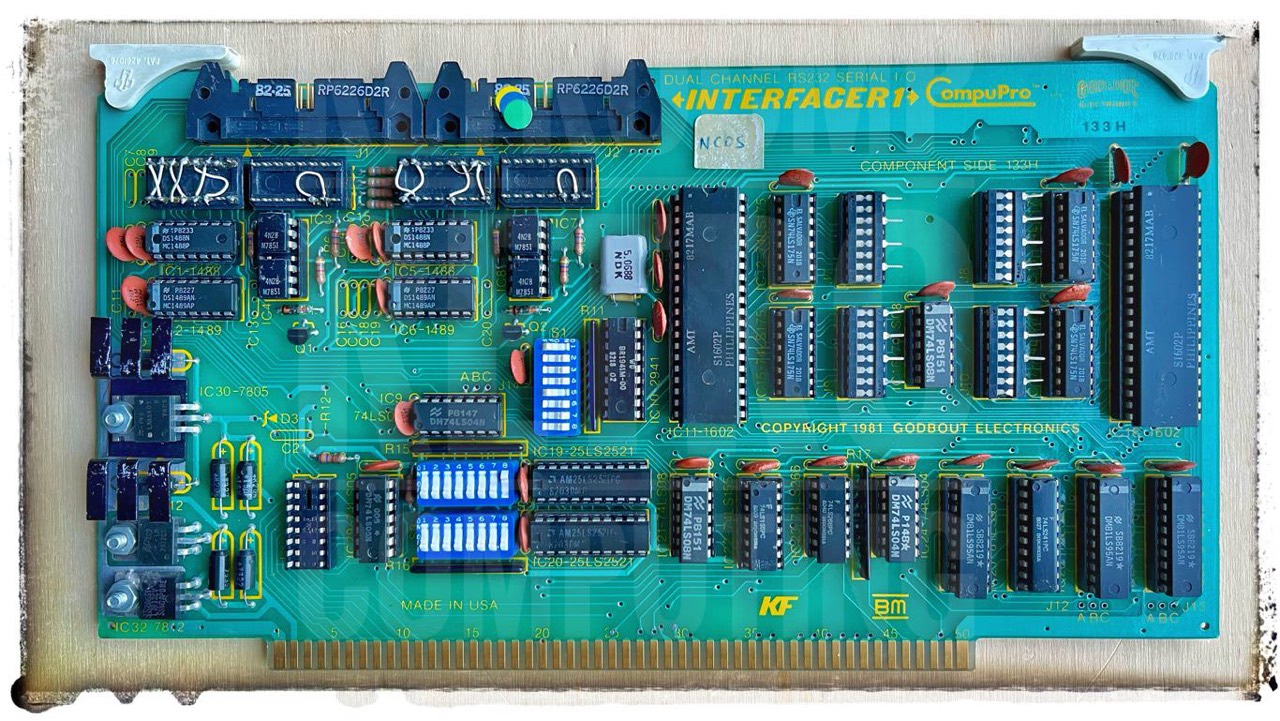

Vector Electronic Company, Sylmar CA

licensed by CompuPro

Back then Vector Electronics Company was located in, 12460 Gladstone Avenue, Sylmar, CA 91342

Settings

Yes, you can use the CompuPro Interface1 as a replacement for the IMSAI SIO-2. But here are some pitfalls to cope with!

Pin 20 - Pin 70

If you want to use the Interfacer1 in an IMSAI 8080 (or Altair 8800) you have to tape pin 70 (and 20); pin 70 is grounded! If you do not, the frontpanel will not work! The Interfacer1 follows the IEEE 696 standard, this is not 100% compatible with the S-100 IMSAI/ALTAIR standard!

Mike Douglas describes the "fundamental" problem as follows: "The Altair uses pin 20 as memory UNPROTECT and pin 70 as memory PROTECT. These are mutually exclusive positive true signals that go to a cross-coupled SR latch on the 1K board. On power up, the protect state of the 1K board is technically indeterminate, but in reality tends to end up one way or the other more often. On your Horizon, pins 20 and 70 are grounded so both PROTECT and UNPROTECT are permanently de-asserted. This, in turn, means the 1K board will remain in the protect/unprotect state into which it fell at power up. In the case of your board, this tends to be protected. This means writes are blocked and your memory test fails. When you cover pins 20 and 70, both PROTECT and UNPROTECT appear high (asserted) to the 1K board, and because of the way the logic is wired, this invalid state enables writes and your board then works."

I/O Address Assignment

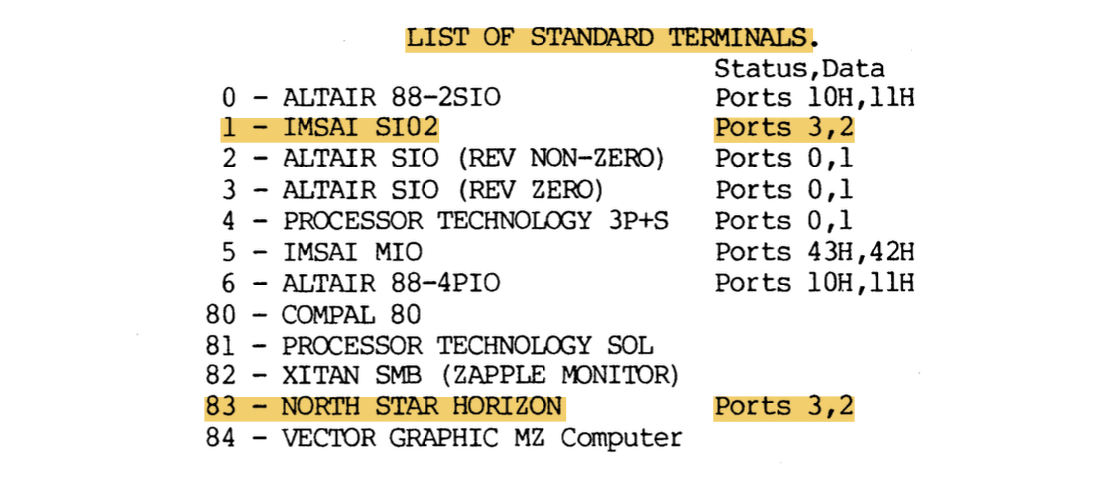

The addressing of the two ports A and B is quite simple, very flexible and is carried out via the DIP switches S2 and S3. However, you need to know how the status and data ports are addressed in your system.

What comes first? STATUS first, data port last (common with MITS, Processor Technology, etc. software) or DATA first, status port last (common with IMSAI software). This setting is made via jumper J14 (ABC). If there is no jumper on the board, the standard setting B-C (IMSAI, data first, status port last) applies. If not, refer to the manual and make the appropriate (very simple) modification.

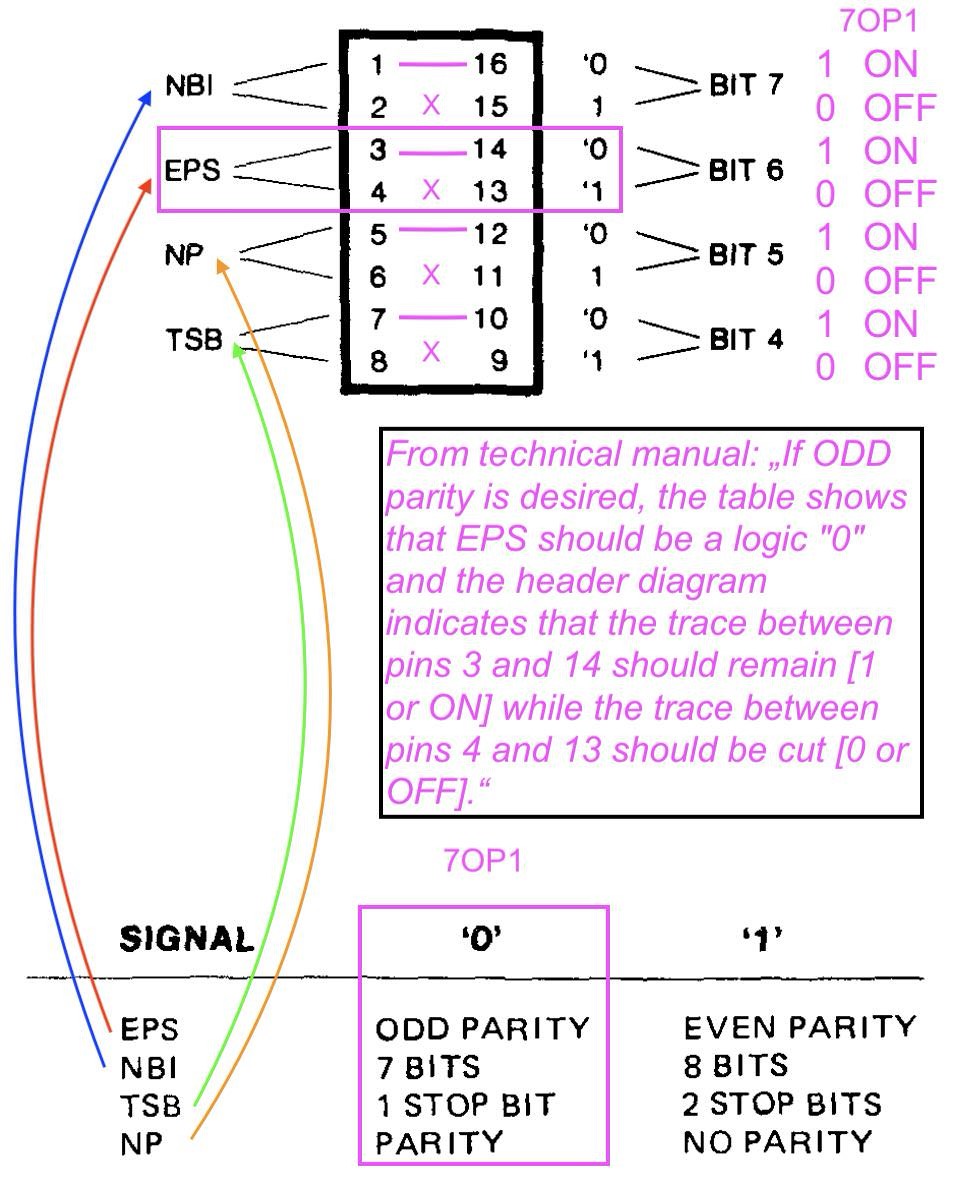

J3, J4, J5, J6 - Serial Mode

Use RS232C - Slave mode settings to connect your terminal (ex. Windows 10, TeraTerm)

J7 & J8 - UART

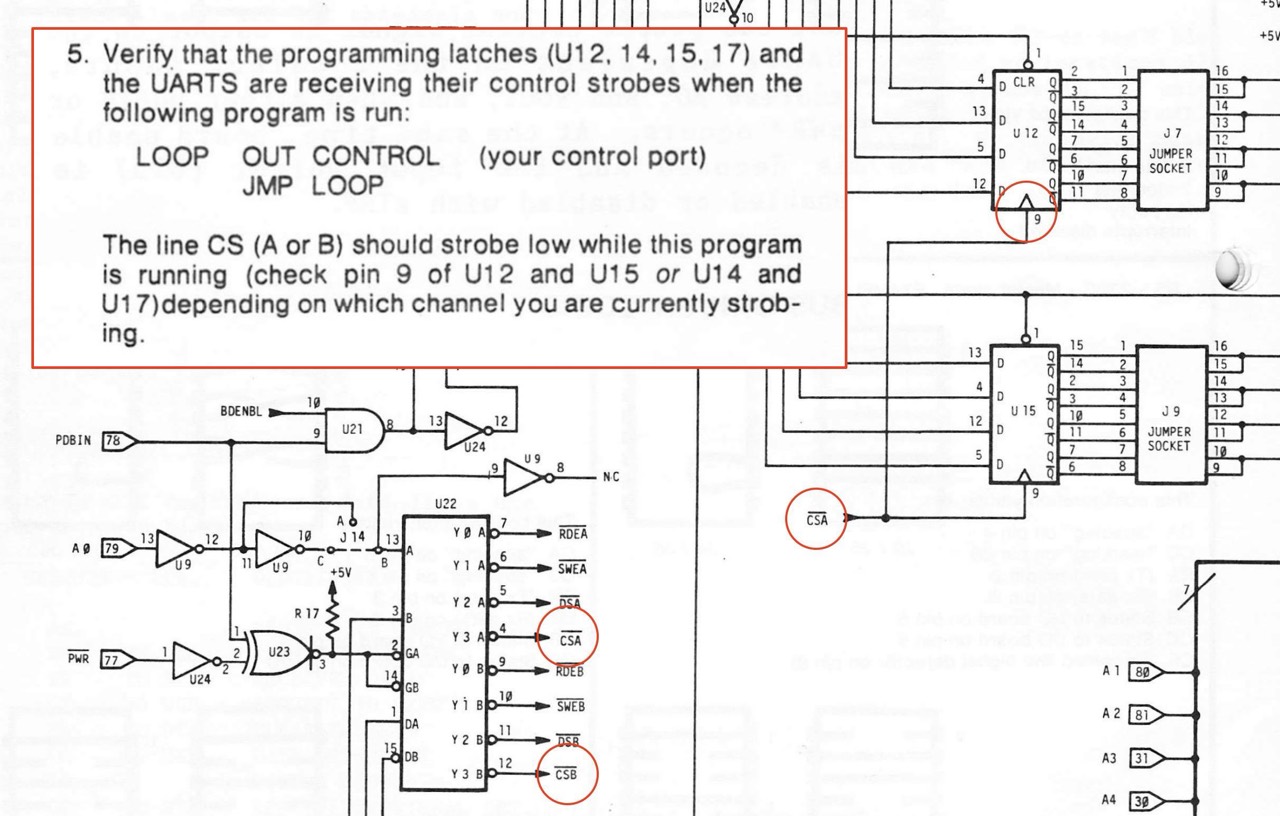

The following quote from Martin Eberhard is very important.

Control bits are configured with jumpers. The board will XOR whatever you write to the control port with the jumper setting. This assumes all jumpers are set to 0. [2]

I run this board with the jumpers (J7/J8) only. I have therefore bent up pins 9 (CSA, CSB) of U12 and U14 (both 74LS175) so that nothing can be written to the control register. So far, this solution (from Mike Douglas) has worked very well. Both MEMON/80, Lifeboat CP/M 24K and PCGET/PCPUT work. This was not the case before.

J7/J8

--------------------------------------------------------

signal logic (0) (1)

--------------------------------------------------------

1 16 0 (1)

NBI bit 7 7 bits 8 bits

2 15 1 (1)

3 14 0 (1)

EPS bit 6 odd parity even parity

4 13 1 (1)

5 12 0 (1)

NP bit 5 parity no parity

6 11 1 (1)

7 10 0 (1)

TSB bit 4 1 stop bit 2 stop bits

8 09 1 (1)

--------------------------------------------------------

7OP1 = 1-0 1-0 1-0 1-0

7EP2 = 1-0 0-1 1-0 0-1

8_N1 = 0-1 1-0 0-1 1-0 or

8_N1 = 0-1 0-1 0-1 1-0

J7 & J9 - Interrupts

I do not use vectored interrupts; J9 and J10 are all set to logic "0" (in my case): 1-0 1-0 1-0 1-0

J9/J10

--------------------------------------------------------

signal 0 1

--------------------------------------------------------

1 16 0 (1) (0)

CA bit 3 disabled enabled

2 15 1 (0) (1)

3 14 0 (1) (0)

CD bit 2 disabled enabled

4 13 1 (0) (1)

5 12 0 (1) (0)

TxINT E bit 1 spacing marking

6 11 1 (0) (1)

7 10 0 (1) (0)

RxINT E bit 0 spacing marking

8 09 1 (0) (1)

--------------------------------------------------------

Tests

Unfortunately, my IMSAI does not yet have an SIO card (IMSAI SIO-2) or a floppy disk controller. Therefore, I have only been able to test the basic functions with the front panel and the IMSAI RAM-4A. This also has its advantages. I have learned a lot.

The next step is to use a good monitor program. A very good program is provided by Martin Eberhard and is called MEMON/80. If you don't know who Martin Eberhard is, search for the two founders of Tesla.

In this first step, I only need the monitor to see if my two Interfacer1 cards are working. The rest will come later.

MEMON/80

---------------------------------------------------------

CIFAC equ TRUE ;Compupro Interfacer 1 (Port A or B)

TIFAC equ TRUE ;Compupro Interfacer 1 (Port A or B)

; Compupro Interfacer 1 Port A 00h 00h-03h ***

; Port B 02h

CBASE equ 000h ;Console Port base address

TBASE equ 002h ;Transfer Port base address

---------------------------------------------------------

FACTORY settings: IMPORTANT!

"As shipped, both channels A and B will have the DATA port

residing at the port address, and the STATUS port residing

at the port address + 1."

=> CDATA = CBASE = 00h => port A

=> CSTAT = CBASE+1 = 01h

=> TDATA = TBASE = 02h => port B

=> TSTAT = TBASE+1 = 03h

---------------------------------------------------------

My J14 mod: just the other way round for MEMON/80!

"If desired, this board may be jumpered so that both channels

have their STATUS ports at the selected address and the DATA

ports at the selected address + 1. This may be accomplished

by cutting the trace between points "B" and "C" at J14 (on

the solder side of the board) and installing a jumper between

points "A" and "B"."

=> CSTAT = CBASE = 00h => port A

=> CDATA = CBASE+1 = 01h

=> TSTAT = TBASE = 02h => port B

=> TDATA = TBASE+1 = 03h

;============================================---------------

;= 3. Specify Memon/80's Memory Utilization =

;============================================

;These specify where Memon/80 is place in memory and where

;its buffers, stack, and variables are. Additionally, you

;can disable some Memon/80 features to reduce the code size.

;-----------------------------------------------------------

;MEBASE equ 0F800h ;Base address of Memon/80 code

MEBASE equ 0C000h ;same as on my N*

;--------------------------------------------------------

;Compupro Interfacer 1 Equates

;

;The Interfacer 1 is built around a pair of 1602-type

;generic UARTs, with jumper selectable baud rate

;generators and with external logic providing status

;and control registers.

;

;Control bits are configured with jumpers. The board will

;XOR whatever you write to the control port with the

;jumper setting. This assumes all jumpers are set to 0.

;--------------------------------------------------------

if CIFAC

CSTAT equ CBASE ;Console STATUS

CCTRL equ CBASE ;Console control

CDATA equ CBASE+1 ;Console DATA

CTXRDY equ 01h ;channel a Tx ready bit

CRXRDY equ 02h ;channel a Rx ready bit

endif ;CIFAC

if TIFAC

TPORT set TRUE ;Transfer port is defined

TSTAT equ TBASE ;Transfer Port status

TCTRL equ TBASE ;Transfer Port control

TDATA equ TBASE+1 ;Transfer Port data

TTXRDY equ 01h ;channel B Tx ready bit

TRXRDY equ 02h ;channel B Rx ready bit

endif ;TIFAC

if CIFAC or TIFAC

IFRST equ 0ACH ;reset: 8 data, no parity, flow

;..control outputs high, no ints

endif ;CIFAC or TIFAC

;--------------------------------------------

;Initialize both Compupro Interfacer channels

;--------------------------------------------

if CIFAC or TIFAC

mvi a,IFRST

endif ;CIFAC or TIFAC

if CIFAC

out CCTRL

endif ;CIFAC

if TIFAC

out TCTRL

endif ;TIFAC

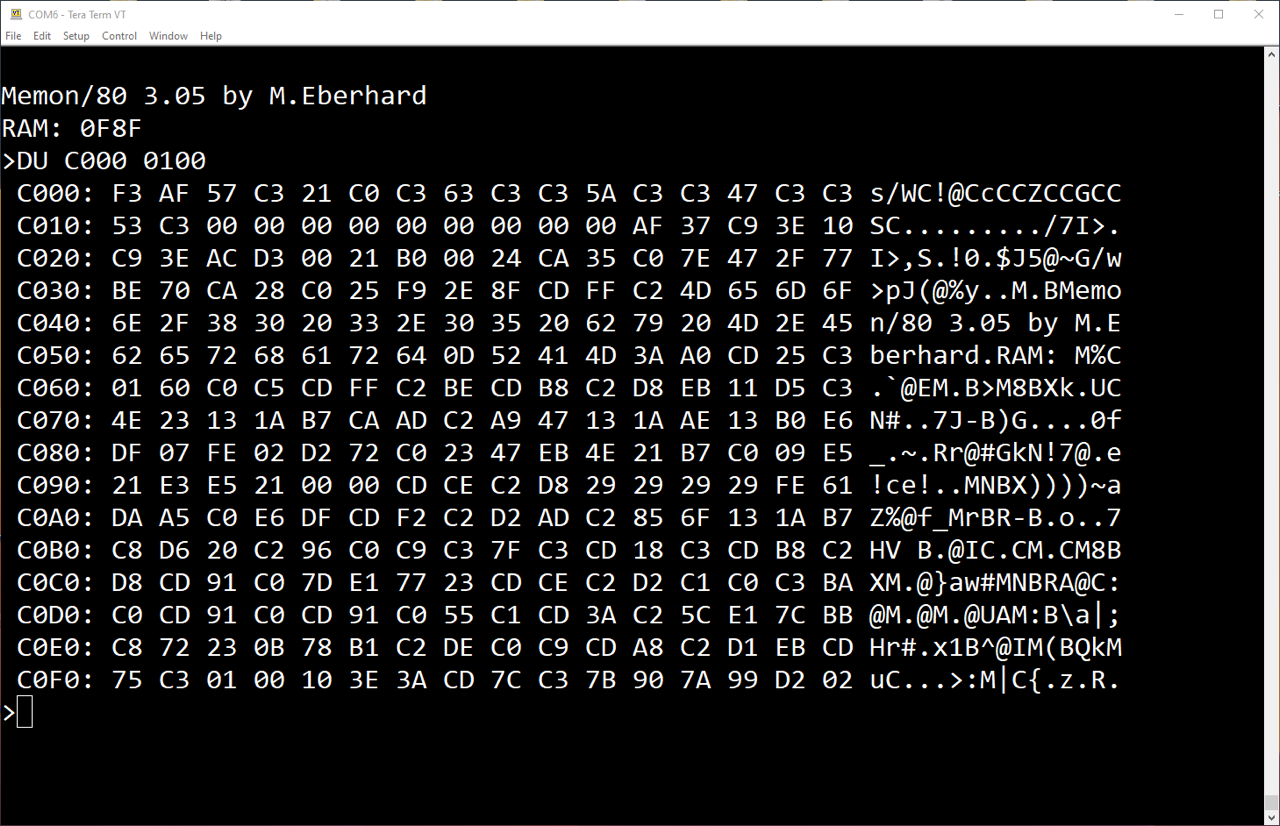

And this is what it looks like when the monitor program is running in combination with the SIO card.

As already mentioned, this is only a first test. In the current example, I am only using a 4K RAM card and I have set the start address of MEMON/80 to C000. I used a 2708 (1K) EPROM and my Cromemco BYTESAVER 8K. Later I will use a 2716 (2K) EPROM with my Solid State Music PB1 board or just split the 2K ROM in two 1K and use the first two sockets in the Cromemco BYTESAVER 8K. In the end, it doesn't matter.

Lifeboat 24K CP/M - IMSAI SIO-2

With the small change to J14 (cut B-C, jumper A-B), MEMON/80 works perfectly, but ... Lifeboat 24K CP/M does not start. Oops! Lifeboat requires DATA at 02h and STATUS at 03h, i.e. the original state of the Interface1.

What to do? I changed both ports; it works.

if CIFAC

;CSTAT equ CBASE ;Console status

;CCTRL equ CBASE ;Console control

;CDATA equ CBASE+1 ;Console data

;--------------------------------------------------------

;Just the other way round for IMSAI SIO-2 and Lifeboat

;tbr, 26.12.2023

;--------------------------------------------------------

CDATA equ CBASE ;Console data

CCTRL equ CBASE+1 ;Console control

CSTAT equ CBASE+1 ;Console status

My IMSAI is running now with the Interfacer1, MEMON/80, N* MDS und Lifeboat CP/M.

Internal Links

External Links

- S100 Computers: CompuPro Interfacer1

Technical Manuals

Others

- Roberts, Steven K.: Sweetening the Bytesaver, Kilobaud Microcomputing, Oct 1979, page 176ff